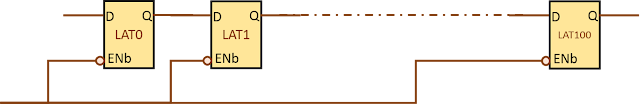

Problem: 100 latches (either all

positive or all negative) are placed in series (figure 1). How many cycles of latency will

it introduce?

|

| Figure 1 : 100 negative level-sensitive latches in series |

As we know, setup check between latches of same polarity (both positive or negative) is zero cycle with half cycle of time borrow allowed as shown in figure 2 below for negative level-sensitive latches:

|

| Figure 2: Setup check between two negative level-sensitive latches |

So, if there are

a number of same polarity latches, all will form zero cycle setup check with

the next latch; resulting in overall zero cycle phase shift.

As is shown in

figure 3, all the latches in series are borrowing time, but allowing any actual

phase shift to happen. If we have a design with all latches, there cannot be a

next state calculation if all the latches are either positive level-sensitive

or negative level-sensitive. In other words, for state-machine implementation,

there should not be latches of same polarity in series.

|

| Figure 3 : Timing for 100 latches in series |

Also read: