In the post (Setup and hold – basics of timinganalysis), we introduced setup and hold timing requirements and also discussed

why these requirements are needed to be applied. In this post, we will be

discussing how these checks are applied for different cases for paths starting

from flops and ending at latches and vice-versa.

Present day designs are focused mainly on the paths

between flip-flops as the elements dominating in them are flip-flops. But there

are also some level-sensitive elements involved in data transfer in current-day

designs. So, we need to have knowledge of setup and hold checks for

flop-to-latch and latch-to-flop paths too. In this post, we will be discussing the

former case. In totality, there can be total 4 cases involved in flop-to-latch

paths as discussed below:

1)

Paths launching from positive

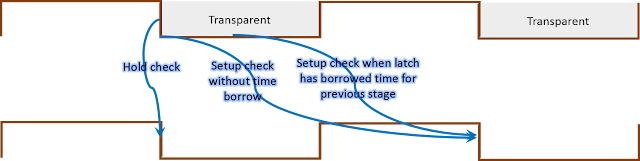

edge-triggered flip-flop and being captured at positive level-sensitive latch: Figure 1 shows a path being

launched from a positive edge-triggered flop and being captured on a positive

level-sensitive latch. In this case, setup check is on the same rising edge (without time borrow) and next falling edge (with time borrow) and

hold check on the previous falling edge with respect to the edge at which data is

launched by the launching flop.

|

Figure 1: Timing path from positive edge flop

to positive level latch

|

Figure below shows the waveforms for setup and hold

checks in case of paths starting from a positive edge triggered flip-flop and

ending at a positive level sensitive latch. As can be figured out, setup and

hold check equations can be described as:

Tck->q +

Tprop + Tsetup < Tskew + Tperiod/2 (for setup

check)

Tck->q +

Tprop > Thold + Tskew - (Tperiod/2) (for hold check)

2)

Paths launching from positive

edge-triggered flip-flop and being captured at negative level-sensitive latch: Figure 3 shows a path starting

from positive edge-triggered flip-flop and being captured at a negative level

sensitive latch. In this case, setup check is on the next falling edge (without time borrow) and on next positive edge (with time borrow). Hold

check on the same edge with respect to the edge at which data is launched (zero cycle hold check).

|

Figure 3: Path from positive edge flop to negative

level latch

|

Figure below shows the waveforms

for setup and hold checks in case of paths starting from a positive edge

triggered flip-flop and ending at a negative level-sensitive latch. As can be

figured out, setup and hold check equations can be described as:

Tck->q +

Tprop + Tsetup < (Tperiod) + Tskew (for setup check)

Tck->q +

Tprop > Thold + Tskew (for

hold check)

3)

Paths launching from negative

edge-triggered flip-flop and being captured at positive level-sensitive latch: Figure 5 shows a path starting

from negative edge-triggered flip-flop and being captured at a positive level

sensitive latch. In this case, setup check is on the next rising edge (without time borrow) and next falling edge (with time borrow). Hold

check on the next rising edge with respect to the edge at which data is

launched.

|

Figure 5: Path from negative edge flop to

positive level latch

|

Figure below shows the waveforms

for setup and hold checks in case of paths starting from a negative edge

triggered flip-flop and ending at a positive level-sensitive latch. As can be

figured out, setup and hold check equations can be described as:

Tck->q +

Tprop + Tsetup < (Tperiod) + Tskew (for setup check)

Tck->q +

Tprop > Thold + Tskew (for

hold check)

1)

Paths launching from negative

edge-triggered flip-flop and being captured at negative level-sensitive latch: Figure 5 shows a path starting

from negative edge-triggered flip-flop and being captured at a negative level

sensitive latch. In this case, setup check is on the same edge (without time borrow) and on next rising edge (with time borrow). Hold

check on the next rising edge with respect to the edge at which data is

launched.

|

Figure 5: Path from negative edge flop to negative level latch

|

Figure below

shows the waveforms for setup and hold checks in case of paths starting from a negative

edge triggered flip-flop and ending at a negative level-sensitive latch. As can

be figured out, setup and hold check equations can be described as:

Tck->q +

Tprop + Tsetup < Tperiod/2 + Tskew (for

setup check)

Tck->q +

Tprop > Thold + Tskew - (Tperiod/2) (for hold check)