Definition of mux: A multiplexer is a combinational circuit that selects one

out of multiple input signals depending upon the state of select line. A 2^N:1 multiplexer with ‘N’ select lines can select 1 out of 2^N inputs. In other words, the multiplexer connects the output to one of its inputs based upon the value held at the select lines. A multiplexer (or commonly called as MUX) is also termed as data selector. Common functions of a multiplexer include concentrating the multiple data lines onto one single line. It can also be used as a data selector or clock selector.

Multiplexers can be categorized based upon the number of inputs:

- 2-input mux: A 2:1 mux has 2 data input lines and 1 select line. The state of select line decides which of the inputs propagates to the output. The truth table of 2x1 mux is given below. As it shows, when SEL is 1, OUT follows IN2 and when SEL is 0, OUT follows IN1.

|

| Figure 1: Truth table of 2x1 mux |

The logic circuit and symbol of 2x1 mux is shown in figure 2. Let us assume logical area of a 2:1 mux to be A.

|

| Figure 2(a): Logic diagram of 2x1 mux Figure 2(b): Schematic symbol of 2x1 mux |

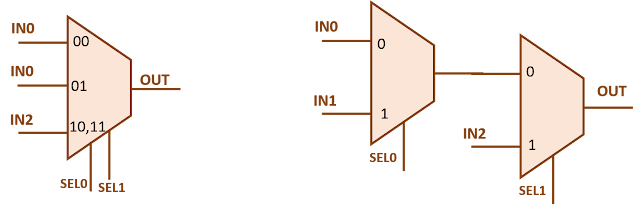

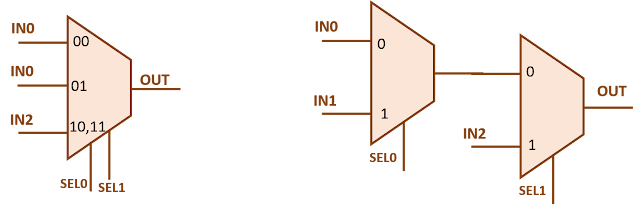

- 3-input mux: A 3:1 mux has 2 select lines and 3 inputs. As a mux with 2 select lines can represent at max 4 inputs, a 3:1 mux repeats some inputs for 2 combinations. The truth table for 3-input mux is given below. As can be seen, for SEL value "10" and "11", IN2 is selected at the output (this is one of the 3 possible scenarios, repetition of IN0 or IN1 is also possible).

|

| Figure 3: Truth table for 3x1 mux |

The schematic symbol and structural representation (in terms of 2x1 muxes) for 3:1 mux is shown in figure 4 below. As can be figured out, 1 3x1 mux can be built using 2 2x1 muxes.

|

| Figure 4(a): Schematic symbol for 3x1 mux Figure 4(b): Structural symbol for 3:1 mux using 2x1 muxes |

- 4-input mux: A 4:1 mux has 2 select lines and 4 inputs. The truth table for 4x1 mux is shown below:

|

| Figure 5: Truth table for 4:1 mux |

Figure 6 below shows the schematic symbol and structural symbol of 4:1 mux using 2:1 muxes. As is evident, a 4:1 mux can be built from 3 2:1 muxes.

|

| Figure 6(a): 4x1 mux schematic symbol Figure 6(b): 4:1 mux structural representation with 2x1 muxes |

- 8-input mux: An 8x1 mux has 3 select lines and 8 inputs. The truth table for 8x1 mux is shown below:

|

| Figure 7: Truth table for 8:1 mux |

The structural representation using 2x1 muxes, and schematic symbol for the same is as shown below in figure 8. An 8-input mux can be implemented using 7 2-input muxes.

|

| Figure 8(a): Schematic symbol for 8x1 mux Figure 8(b): Structure of 8x1 mux with 2x1 mux |

- 16-input mux: A 16x1 mux can be implemented from 15 2:1 muxes. It has 4 select lines and 16 inputs. Output follows one of the inputs depending upon the state of the select lines.

Also read: