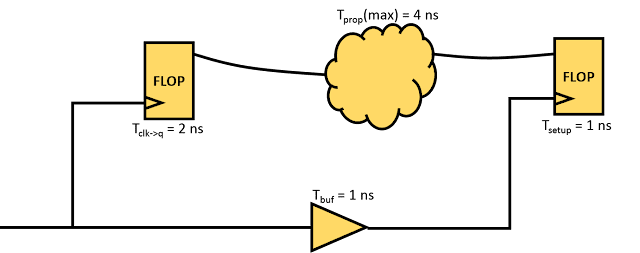

The above timing path is a single cycle timing path. The maximum frequency is governed by setup timing equation. In other words, maximum frequency of operation is the maximum frequency (minimum time period of clock) that satisfies the following condition:

Tck->q + Tprop + Tsetup - Tskew < Tperiod

Here,

Tck->q = 2 ns, Tprop = 4 ns, Tsetup = 1 ns, Tskew = 1 ns, Tperiod

Now,

Tperiod > 2 ns + 4 ns + 1 ns - 1 ns

Tperiod > 6 ns

So, the minimum time period of the clock required is 6 ns. And the maximum frequency that the above circuit can work is (1000/6) MHz = 166.67 MHz.

It should be noted that at if we operate this timing path at maximum frequency calculated, setup slack will be zero. :-)

In this post, we talked about frequency of operation of single cycle timing paths. Can you figure out maximum frequency of operation for half cycle timing paths? Also, there is a relation of maximum operating frequency to hold timing? Can you think about this situation?

Also read: