What are lock-up latches: Lock-up

latch is an important element in scan-based designs, especially for

hold timing closure of shift modes. Lock-up latches are necessary to avoid skew

problems during shift phase of scan-based testing. A lock-up latch is nothing

more than a transparent latch used intelligently in the places where clock skew

is very large and meeting hold timing is a challenge due to large uncommon

clock path. That is why, lockup latches are used to connect two flops in scan

chain having excessive clock skews/uncommon clock paths as the probability of

hold failure is high in such cases. For instances, the launching and capturing

flops may belong to two different domains (as shown in figure below).

Functionally, they might not be interacting. Hence, the clock of these two

domains will not be balanced and will have large uncommon path. But in

scan-shift mode, these interact shifting the data in and out. Had there been no

lockup latches, it would have been very difficult for STA engineer to close

timing in a scan chain across domains. Also, probability of chip failure would

have been high as there a large uncommon path between the clocks of the two

flops leading to large on-chip-variations. That is why; lockup latches can be referred as as the soul mate of scan-based designs.

|

|

Figure 1 : Lockup latches - the soul

mate of scan-based designs

|

Where to use a lock-up

latch: As mentioned above, a lock-up latch is used where

there is high probability of hold failure in scan-shift modes. So, possible

scenarios where lockup latches are to be inserted are:

- Scan chains from different clock domains: In this case, since, the two domains do not interact functionally, so both the clock skew and uncommon clock path will be large.

- Flops within same domain, but at remote places: Flops within a scan chain which are at remote places are likely to have more uncommon clock path.

|

|

Figure

2: A path crossing from domain

1 to domain 2 (scope for a lock-up latch insertion)

|

|

|

Figure

3: Timing diagram showing setup and

hold checks for path crossing from domain 1 to domain 2

|

Positive or negative level

latch?? It depends on the path you are inserting a

lock-up latch. Since, lock-up latches are inserted for hold timing; these are not

needed where the path starts at a positive edge-triggered flop and ends at a

negative edge-triggered flop. It is to be noted that you will never find scan paths originating at positive edge-triggered flop and ending at negative edge-triggered flop due to DFT specific reasons. Similarly, these are not needed where path starts

at a negative edge-triggered flop and ends at a positive edge-triggered flop.

For rest two kinds of flop-to-flop paths, lockup latches are required. The

polarity of the lockup latch needs to be such that it remains open during the

inactive phase of the clock. Hence,

- For flops triggering on positive edge of the clock, you need to have latch transparent when clock is low (negative level-sensitive lockup latch)

- For flops triggering on negative edge of the clock, you need to have latch transparent when clock is high (positive level-sensitive lockup latch)

Who inserts a lock-up latch:

These days, tools exist that automatically add lockup latches where a scan

chain is crossing domains. However, for cases where a lockup latch is to be

inserted in an intra-domain scan chain (i.e. for flops having uncommon path),

it has to be inserted during physical implementation itself as physical

information is not feasible during scan chain implementation (scan chain

implementation is carried out at the synthesis stage itself).

Which clock should be connected to lock-up latch: There are two possible ways in which we can connect the clock pin of the lockup latch inserted. It can either have same clock as launching flop or capturing flop. Connecting the clock pin of lockup latch to clock of capturing flop will not solve the problem as discussed below.

Which clock should be connected to lock-up latch: There are two possible ways in which we can connect the clock pin of the lockup latch inserted. It can either have same clock as launching flop or capturing flop. Connecting the clock pin of lockup latch to clock of capturing flop will not solve the problem as discussed below.

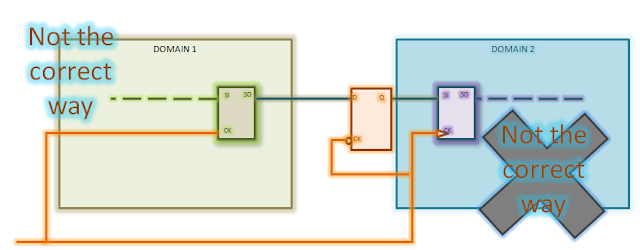

- Lock-up latch and capturing flop having the same clock (Will not solve the problem): In this case, the setup and hold checks will be as shown in figure 5. As is apparent from the waveforms, the hold check between domain1 flop and lockup latch is still the same as it was between domain 1 flop and domain 2 flop before. So, this is not the correct way to insert lockup latch.

|

|

Figure

4: Lock-up latch clock pin

connected to clock of capturing flop

|

|

|

Figure

5: Timing diagrams for figure 4

|

- Lock-up latch and launching flop having the same clock: As shown in figure 7, connecting the lockup latch to launch flop’s clock causes the skew to reduce between the domain1 flop and lockup latch. This hold check can be easily met as both skew and uncommon clock path is low. The hold check between lockup latch and domain2 flop is already relaxed as it is half cycle check. So, we can say that the correct way to insert a lockup latch is to insert it closer to launching flop and connect the launch domain clock to its clock pin.

|

|

Figure

6: Lock-up latch clock pin

connected to clock of launch flop

|

|

|

Figure

7: Waveforms for figure 6

|

Why don’t we add buffers: If

the clock skew is large at places, it will take a number of buffers to meet

hold requirement. In normal scenario, the number of buffers will become so

large that it will become a concern for power and area. Also, since

skew/uncommon clock path is large, the variation due to OCV will be high. So,

it is recommended to have a bigger margin for hold while signing it off for

timing. Lock-up latch provides an area and power efficient solution for what a

number of buffers together will not be able to achieve.

Advantages of inserting

lockup latches:

- Inserting lock-up latches helps in easier hold timing closure for scan-shift mode

- Robust method of hold timing closure where uncommon path is high between launch and capture flops

- Power efficient and area efficient

- It improves yield as it enables the device to handle more variations.

Lockup registers: Instead of latches, registers can also be used as lockup elements; however, they have their own advantages and disadvantages. Please refer to Lockup latches vs. lockup registers : what to chose for a comparative study of using lockup latches vs lockup registers.

References:

1) “Why not add buffer but lockup latch” - http://www.edaboard.com/thread82364.html

Also read:

- Setup and hold checks for latch-to-flop and flop-to-latch paths

- Controllability and observability - the two DFT principles

- On-chip variations - the STA takeaway

- Setup and hold - basics of timing analysis

- Interesting problem - latches in series

Do we need to insert lockup latches in case capturing clock is built at lesser latency?

ReplyDeleteAs mentioned above, there are two cases in which lockup latches need to be inserted - skew and uncommon path. If we consider ideal scenario, there should not be the need. However, due to on-chip variations, the variation in launch and capture path may be very large. So, if launch and capture path have large uncommon path, even if the capture flop is built at lesser latency; in real silicon scenario, it may exceed the latency of launch clock path. Hence, it is better if we have a lockup latch for better yield.

ReplyDeletewhat do you mean by uncommon clock path?

DeleteThe clock of launch and capture registers of interacting timing paths normally starts from a common source. However, depending upon the placement and clock path logic, it has to branch out somewhere. Till the point where it branches out is common clock path. And afterwards, it is said to be uncommon clock path. I hope I am making sense.

DeleteSuper explanation.. Thanks

ReplyDeleteHi,

ReplyDeleteWhy lockup latch is not necessary where the path starts at a positive edge-triggered flop and ends at a negative edge-triggered flop?

Because there is already half cycle hold margin in this path. So, looking at the timing, we do not require lockup latch here. However, due to DFT specific reasons, lockup latch is required here.

DeleteHi ,

DeleteSuppose i have scenario where posedge flop followed by edge flop. Since scanclk frequence is less and we could still meet the half cycle timing, why still we need lockup latch. Could you please explain more in DFT reason why it required.

Thanks in Advance

Hi,

DeleteSuppose if i stitch posedge followed by negege, as DFT specific reason, needs to insert LL. Could you please explain more what are these specific reasons

Thanks in Advance

Hi

DeleteThe answer lies in the basics of how DFT works. If you know the specifics, tester forces data only once during every scan cycle, and observes the data only once. Now, if there is a stuckat fault, for instance, the negative flop and positive flop would always have the same value. So, you can never have a pattern with 01 or 10 on these. Yes, you can work around for such cases, but, it would require intricate level monitoring of functional paths, and may change with every iteration of scan stitching.

I hope it helps. :-)

great article. few questions. Can PnR tool insert Lock up latches.. Because synthesis does not understand Clock tree and uncommon branches.

ReplyDeleteYes, there may exist such tools. But you can scriptize the insertion of lockup latches, and the scripts are, in a way, small tools only. :-)

Deletealso can you send me the article lock up latches vs lock up flops. The link is dead

ReplyDeleteI updated it, thanks for pointing it out.

DeleteAlso you say "Who inserts a lock-up latch: These days, tools exist that automatically add lockup latches where a scan chain is crossing domains. However, for cases where a lockup latch is to be inserted in an intra-domain scan chain (i.e. for flops having uncommon path), it has to be inserted during physical implementation itself as physical information is not feasible during scan chain implementation (scan chain implementation is carried out at the synthesis stage itself)."

ReplyDeleteI have not seen an option in the place and route tool to add a lockup latch.

You need to add lockup latches specifically through netlist editing commands of PnR tools; for instance add_inst, add_net etc.

DeleteI must thank you for the post!

ReplyDeletelets say someone added lock up latch in the design, where it is not required , that means it is redundant, and we want to make it bypass, then how to do that check ,

ReplyDeleteHi

DeleteI dont think bypassing a redundant lockup latch will be of any help in terms of area, power or timing. Of course, it will make sense if you want to remove it.

First check, of course, should be to check valid lockup latch cases, for example if a lockup latch is inserted between neg_flop -> pos_flop paths, you can remove it.

Another level of check can be latency of latch, launch flop and capture flop. If launch flop is built at a much larget latency than capture flop, ideally, you can remove that lockup latch.

Since you have inserted negative latch, in fig7 how come hold is calculated in the positive edge of the clock(latch clock waveform) ?

ReplyDeleteHi

DeleteHold to a negative latch is always checked on positive edge of the clock

Is a lockup latch needed between a negative launch flop and positive capture flop when the clock domains are asynchronous? A lockup latch can tolerate skews only if they are less than half the clock period. Different tools do not insert for such cases but what if the skew is large enough?

ReplyDeleteYou should not design for such cases if skew is more than half clock period. And half clock period skew is a lot.

DeleteEven if we assume hypothetically that skew is more than half clock cycle, then the only solution in my opinion is to multiple stages of lockup flops (pos -> neg -> pos ...) and each stage separated by a skew less than half clock cycle. *But that kind of design is an overkill.

If you modify figure 4 to a high phase latch (place it in the capturing domain), will that behave as a lock up latch? & Will it solve the problem?

ReplyDeleteYes, it will still behave as a lockup latch & solve the shift problem. But it will be more complex to handle in atspeed timing than a negative level latch tied to launch domain.

DeleteThanks a lot for your artical . But I have 2 questions :

ReplyDelete1. how does this situation happen the skew between these two flops become large? In my opinion ,if they have timing checks ,during clock tree synthesis (especially scan clock) , tool will try to balance their skew.

2. will inserting look_up latch affect logic equivalent check (LEC) or not ?

Hi

Delete1. Yes, cts tool tries to balance the skew. But there can be scan crossing between asynchronous functional clocks. This will not be balanced by the tool.

2. I have tried to answer here.

https://vlsiuniverse.blogspot.com/2023/05/does-inserting-lockup-latch-affect.html?m=1

Thanks for the explaination.

ReplyDeleteWhy can we add latches in scan paths only. Cant we add them to fix hold in functional paths ? any reason behind it.

Hi

DeleteYes you can add latches in functional path as well to fix hold issues, but you have to be extremely cautious in doing so. The major reasons/precautions listed below:

1. Scan paths are not covered in LEC, hence, you can add any number of lockup latches in netlist without any need to modify the RTL. This is not true in case of functional path. Any such latch addition will need RTL update.

2. There might be a corner-case scenario that might get triggered with latch addition. Examples could be reset value not propagating through latch. Hence, even on adding a single latch, you need to verify all testcases for functionality.

I hope I was able to answer your question.

Thanks for the great article. Regarding polarity of lock up latch, you mentioned for flops triggering on positive edge of the clock, you need to have a negative level-sensitive lockup latch. In this case if we insert a positive level triggered latch at capture domain, that also works. Do we always insert opposite polarity latch?

ReplyDeleteHi

DeleteI have answered your query in my latest post, I apologize for taking long time. I hope it answers your question.

https://vlsiuniverse.blogspot.com/2025/01/why-there-needs-to-be-lockup-latch.html

If clk1 is half cycle delayed with respect to clk2.Here lockup latch is required or not?

ReplyDeleteNot required since you should have sufficient positive hold margin to cover for variations in my opinion, since hold check is zero cycle in this case.

Delete