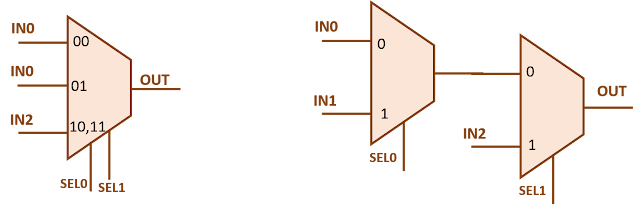

Definition of a multiplexer: A 2^n-input mux has n select lines. It can be used to implement logic functions by implementing LUT (Look-Up Table) for that function. A 2-input mux can implement any 2-input function, a 4-input mux can implement any 3-input, an 8-input mux can implement any 4-input function, and so on. This property of muxes makes FPGAs implement programmable hardware with the help of LUT muxes. In this post, we will be discussing the implementation of 2-input AND, OR, NAND, NOR, XOR and XNOR gates using a 2-input mux.

2-input AND gate implementation using 2:1 mux: Figure 1 below shows the truth table of a 2-input AND gate. If we observe carefully, OUT equals '0' when A is '0'. And OUT follows B when A is '1'. So, if we connect A to the select pin of a 2:1 mux, AND gate will be implemented if we connect D0 to '0' and D1 to 'B'.

|

| Figure 1: Truth table of AND gate |

|

| Figure 2: Implementation of AND gate using a 2:1 mux |

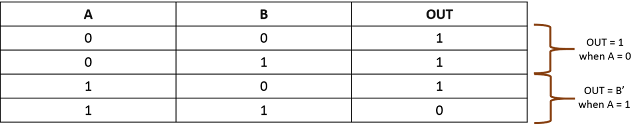

2-input NAND gate using 2:1 mux: Figure 3 below shows the truth table of a 2-input NAND gate. If we observe carefully, OUT equals '1' when A is '0'. Similarly, when A is '1', OUT is B'. So, if we connect SEL pin of mux to A, D0 pin of mux to '1' and D1 to B', then it will act as a NAND gate.

|

| Figure 3: Truth table of 2-input NAND gate |

Figure 4 below shows the implementation of a 2-input NAND gate using 2:1 mux.

|

| Figure 4: Implementation of 2-input NAND gate using 2:1 mux |

2-input OR gate using 2x1 mux: Figure 5 below shows the truth table for a 2-input OR gate. If we observe carefully, OUT equals B when A is '0'. Similarly, OUT is '1' (or A), when A is '1'. So, we can make a 2:1 mux act like a 2-input OR gate, if we connect D0 pin to B and D1 pin to A, with select connected to A.

|

| Figure 5: Truth table of 2-input OR gate |

Figure 6 below shows the implementation of 2-input OR gate using a 2:1 multilpexer:

|

| Figure 6: Implementation of 2-input OR gate using 2:1 mux |

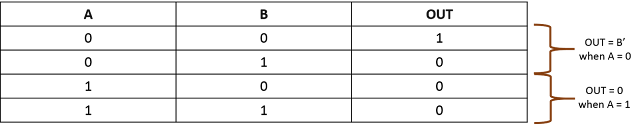

2-input NOR gate using 2x1 mux: Figure 7 below shows the truth table of a 2-input NOR gate. If we observe carefully, OUT equal B' when A is '0'. Similarly, OUT equals '0' when A is '1'. So, we can make a 2-input mux act like a 2-input NOR gate, if we connect SEL of mux to A, D0 to B' and D1 to '0'.

|

| Figure 7: Truth table of 2-input NOR gate |

|

| Figure 8: Implementation of 2-input NOR gate using 2x1 mux |

2-input XNOR gate using 2x1 mux: Figure 9 below shows the truth table of a 2-input XNOR gate. If we observe carefully, OUT equals B' when A is '0' and equals B when A is '1'. So, a 2-input XNOR gate can be implemented from a 2x1 mux, if we connect SEL pin to A, D0 to B' and D1 to B.

|

| Figure 9: Truth table of 2-input XNOR gate |

The implementation of 2-input XNOR gate using a 2x1 mux is as shown in figure 10.

|

| Figure 10: Implementation of 2-input XNOR gate using 2x1 mux |

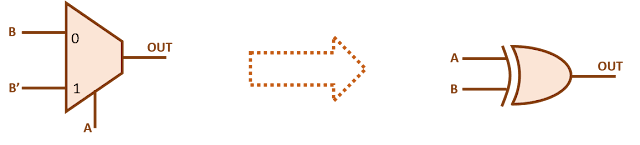

2-input XOR gate using 2x1 mux: Figure 11 shows the truth table for a 2-input XOR gate. If we observe carefully, OUT equals B when A is '0' and B' when A is '1'. So, a 2:1 mux can be used to implement 2-input XOR gate if we connect SEL to A, D0 to B and D1 to B'.

|

| Figure 11: Truth table of 2-input XOR gate |

Figure 12 shows the implementation of 2-input XOR gate using 2x1 mux.

|

| Implementation of 2-input XOR gate using 2x1 mux |

NOT gate using 2:1 mux: Figure 13 shows the truth table for a NOT gate. The only inverting path in a multiplexer is from select to output. To implement NOT gate with the help of a mux, we just need to enable this inverting path. This will happen if we connect D0 to '1' and D1 to '0'.

|

| Figure 13: Truth table of NOT gate |

Figure 14 shows the implementation of NOT gate using 2x1 mux:

|

Figure 14: Implementation of NOT gate using 2x1 mux

|