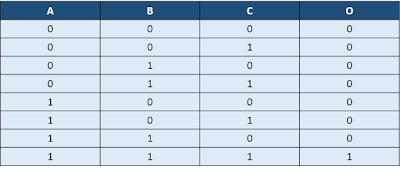

As we know, the logical equation of a 2-input mux is given as below:

De-Morgan's law states that

m + n = (m'n')'

Taking this into account, here m = s'A and n = sB

Y = (s' A + s B)Where s is the select of the multiplexer.

De-Morgan's law states that

m + n = (m'n')'

Taking this into account, here m = s'A and n = sB

Y = ((s'A)'(sB)')' = ((s' A)' (s B)')'

Thus, Y is equal to ((s' nand A) nand (s nand B)). No further optimizations seem possible to this logic. Figure 1 below shows the implementation of 2:1 mux using 2-input NAND gates.