Bubble

error correction is a very common term associated to flash ADCs (see

flash ADC block diagram) wherein the output produced by comparators stage

is expected to be a thermometer code. However, due to multiple non-idealities

and mismatches in comparators and their inputs, the output may not be a symbol

of thermometer code, but has some irregularities. So, the thermometer to binary

converter stage may not be able to convert it to binary code as it is generally

a state machine that accepts only thermometer code as input and may produce a

garbage output if provided some other input that is not thermometer code. There

may be some zeroes in-between a series of ones. For example, the output may be

“01011111” instead of “01111111”. “01011111”, when fed to thermometer to binary

converter will produce garbage value. Either “01111111” should be given or

“00111111” or “00011111”. This will reduce the error. The presence of zeroes in

a series of ones or presence of ones in a series of zeroes in the comparators’

output is termed as bubble error. And the removal of these bubbles from

near-thermometer code is termed as bubble error correction.

Kinds of bubble errors: Bubble

errors are categorized by their order. A first order bubble error means there

is only single ‘1’ between a series of zeroes or vice-versa. For example,

“0010001101” has two first order bubbler, on second bit from right and third

bit from left. Similarly, “01100001111” has a second order bubble.

“00011100000000010111” has one third-order and one first-order bubble.

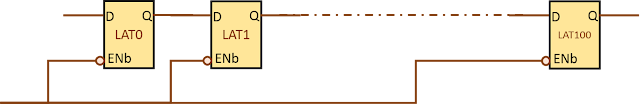

What circuit can be used to correct

bubble errors? The simplest circuit that can be used to correct bubble

errors is majority-of-three circuit. In it, each output is compared with one

output on the left and one on the right. The majority of the three is finally

produced at the output. This is how a near-thermometer code will be converted

to a thermometer code. However, a majority of three circuit will be able to

correct bubble errors of first order only. There are more sophisticated

circuits for second and higher order bubble correction.

Hope you’ve found this post useful. Let us know what you think in the comments.