STA problem: Consider below figure, wherein minimum pulse width requirement of a flip-flop is 590 ps. It is getting clocked by a PLL of 500 MHz with a duty cycle variation of 60 ps. There are 30 buffers in clock path, each having a rise delay of 60 ps and fall delay of 48 ps. Will this setup be able to meet the duty cycle requirement of flip-flop? Find the slack available.

Solution:

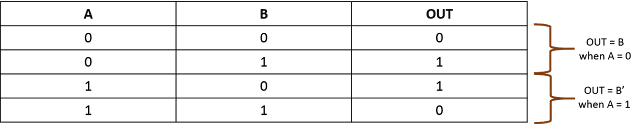

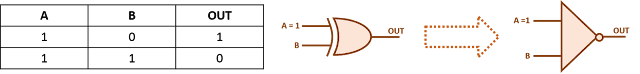

Here, we must remember that pulse can be either high pulse or low pulse. So, we need to check for both. Let us start with high pulse:

Pulse width check for high pulse: Here, we are left with calculating the latest possible arrival of rising edge and earliest possible arrival of falling edge at the flip-flop. It is given that

Ideal clock period = 2000 ps (500 MHz frequency)

Ideal half cycle = 1000 ps

Duty cycle variation of clock source = 60 ps

So, if we assume that positive edge of the clock has arrived at 0 time, negative edge can arrive at any time between 940 ps (1000 - 60) and 1060 ps (1000 + 60). Taking the pessimistic case, we have to assume negative edge arrives at 940 ps thereby making the high pulse as 940 ps at clock source.

Now, there are 30 buffers with rise delay of 60 ps and fall delay of 48 ps.

Rising edge will reach flip-flop at time (0 + 30 * 60) = 1800 ps.

Falling edge will reach flip-flop at time (940 + 30 * 48) = 2380 ps

Effective pulse width visible at flip-flop = 2380 - 1800 = 580 ps

Now, the pulse width requirement = 590 ps

Slack = Actual pulse width = Required minimum pulse width = -10 ps

So, we are violating the minimum high pulse width requirement by 10 ps.

Pulse width requirement for low pulse: Similar to the earlier case, we have to find the difference in arrival of latest negative edge and earliest positive edge.

Ideal clock period = 2000 ps (500 MHz)

Ideal half cycle = 1000 ps

Duty cycle variation of clock source = 60 ps

If we assume that negative edge arrived at 0 ps, positive edge can arrive at any time between 940 ps and 1060 ps. Taking the pessimistic case, low pulse width = 940 ps at clock source.

Now, there are 30 buffers with rise delay of 60 ps and fall delay of 48 ps.

Falling edge will reach flip-flop at time (0 + 30 * 48) = 1440 ps

Rising edge will reach flip-flop at time (940 + 60 * 30) = 2740 ps

Effective pulse width visible at flip-flop = 2740 - 1440 = 1300 ps

Pulse width requirement = 590 ps

Slack = 1300 - 590 = 710 ps

So, we are meeting the low pulse width requirement by 710 ps.