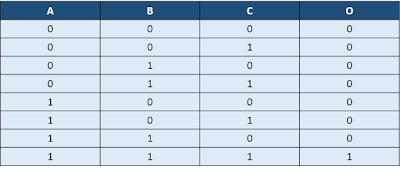

2-input XOR gate using 2x1 mux: Figure 1 shows the truth table for a 2-input XOR gate where A and B are the two inputs and OUT is equal to XOR of A and B. If we observe carefully, OUT equals B when A is '0' and B' when A is '1'. So, a 2:1 mux can be used to implement 2-input XOR gate if we connect SEL to A, D0 to B and D1 to B'.

|

| Figure 1: Truth table of 2-input XOR gate |

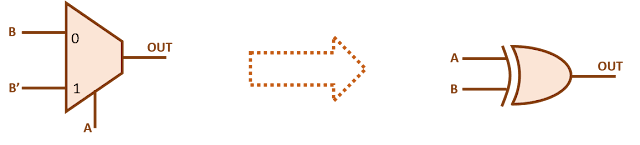

Figure 2 shows the implementation of 2-input XOR gate using 2x1 mux.

Figure 2: Implementation of 2-input XOR gate using 2x1 mux

|

Similarly, we can connect B to select of mux, and get the XOR gate implemented using similar procedure.