False path is a very

common term used in STA. It refers to a timing path which is not required to be

optimized for timing as it will never be required to get captured in a limited time when excited in normal working situation of

the chip. In normal scenario, the signal launched from a flip-flop has to get

captured at another flip-flop in only one clock cycle. However, there are

certain scenarios where it does not matter at what time the signal originating

from the transmitting flop arrives at the receiving flop. The timing path

resulting in such scenarios is labeled as false path and is not optimized for

timing by the optimization tool.

Definition of false path: A timing path, which can get captured even after a very large interval of time has passes, and still, can produce the required output is termed as a false path. A false path, thus, does not need to get timed and can be ignored while doing timing analysis.Common false path scenarios: Below, we list some of the examples , where false paths can be applied:

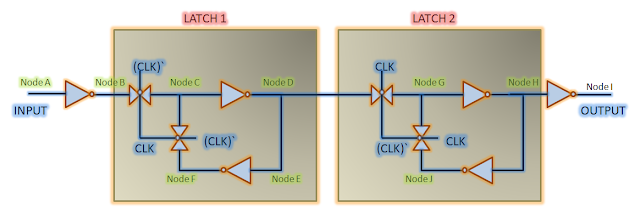

Synchronized signals: Let us say we have a two flop synchronizer placed between a sending and receiving flop (The sending and receiving flops may be working on different clocks or same clock). In this scenario, it is not required to meet timing from launching flop to first stage of synchronizer. Figure 1 below shows a two-flop synchronizer. We can consider the signal coming to flop1 as false, since, even if the signal causes flop1 to be metastable, it will get resolved before next clock edge arrives with the success rate governed by MTBF of the synchronizer. This kind of false path is also known as Clock domain crossing (CDC).

Figure 1: A two flop synchronizer

However, this does not mean that wherever you see a chain of

two flops, there is a false path to first flop. The two flops may be for

pipelining the logic. So, once it is confirmed that there is a synchronizer,

you can specify the signal as false.

Similarly, for other types of synchronizers as well, you can

specify false paths.

False paths for static signals arising due to merging of modes: Suppose you have a structure as shown in figure 1 below. You have two modes, and the path to multiplexer output is different depending upon the mode. However, in order to cover timing for both the modes, you have to keep the “Mode select bit” unconstrained. This result in paths being formed through multiplexer select also. You can specify "set false path" through select of multiplexer as this will be static in both the modes, if there are no special timing requirements related to mode transition on this signal. Specifically speaking, for the scenario shown in figure 1,

False paths for static signals arising due to merging of modes: Suppose you have a structure as shown in figure 1 below. You have two modes, and the path to multiplexer output is different depending upon the mode. However, in order to cover timing for both the modes, you have to keep the “Mode select bit” unconstrained. This result in paths being formed through multiplexer select also. You can specify "set false path" through select of multiplexer as this will be static in both the modes, if there are no special timing requirements related to mode transition on this signal. Specifically speaking, for the scenario shown in figure 1,

Mode 1 : set_case_analysis 0 MUX/SEL

Mode 2 : set_case_analysis 1 MUX/SEL

Mode with Mode1 and Mode2 merged together : set_false_path -through MUX/SEL

Mode 2 : set_case_analysis 1 MUX/SEL

Mode with Mode1 and Mode2 merged together : set_false_path -through MUX/SEL

Figure 2: Mode selection signal

selecting between mode1 and mode2 paths

Architectural

false paths: There are some timing paths that are never possible to

occur. Let us illustrate with the help of a hypothetical, but very simplistic

example that will help understand the scenario. Suppose we have a scenario in

which the select signals of two 2:1 multiplexers are tied to same signal. Thus,

there cannot be a scenario where data through in0 pin of MUX0 can traverse

through in1 pin of MUX1. Hence, it is a false path by design architecture.

Figure 3 below depicts the scenario.

Figure 3: A hypothetical example

showing architectural false path

Specifying false path: The SDC command to specify a timing path as false path is "set_false_path". We can apply false path in following cases:

- From register to register paths

- set_false_path -from regA -to regB

- Paths being launched from one clock and being captured at another

- set_false_path -from [get_clocks clk1] -to [get_clocks clk2]

- Through a signal

- set_false_path -through [get_pins AND1/B]

Also read: