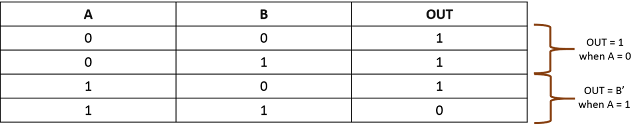

2-input NAND gate using 2:1 mux: Figure 3 below shows the truth table of a 2-input NAND gate. If we observe carefully, OUT equals '1' when A is '0'. Similarly, when A is '1', OUT is B'. So, if we connect SEL pin of mux to A, D0 pin of mux to '1' and D1 to B', then it will act as a NAND gate.

|

| Figure 3: Truth table of 2-input NAND gate |

Figure 4 below shows the implementation of a 2-input NAND gate using 2:1 mux.

|

| Figure 4: Implementation of 2-input NAND gate using 2:1 mux |