Design problem: Make a simple circuit whose output clock is twice in

frequency to the input clock.

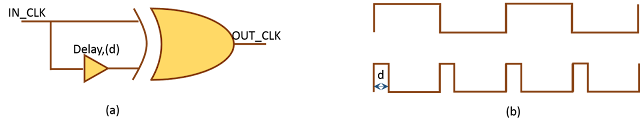

An XOR gate with

one of its input getting delayed version of the other input can act as a

frequency multiplier. Since, an XOR gate produces a ‘0’ when both inputs are

same, and ‘1’ when both inputs are different; if it gets delayed version of one

input at the other, every time input toggles, a pulse is produced at the

output. The duration of the pulse is equal to the delay introduced by delay

element. The circuit and the resulting waveform is shown in figure 1 below. This

circuit arrangement is also known as pulse generator as it produces a pulse on

every toggle of input.

|

| (a) Multiply-by-2 clock circuit (b) Input and output clock waveforms of multiply-by-2 clock circuit |

Characteristics of XOR multiply by 2:

- The output pulse duration is equal to the delay introduced by delay element.

- For duty cycle to be equal to 50%, the delay element’s delay must be half that of input clock. Since, this cannot be guaranteed, the output duty cycle will not be 50%.

- The delay element’s delay must be less than half the input clock period; otherwise it will not work

- The inactive state of XOR multiply-by-2 will be 0 as it produces a '0' when both inputs are same. To implement a multiply-by-2 circuit with '1' as inactive state, you will have to use an XNOR gate.

Hope you’ve found this post useful. Let us know what you think in the comments.

Also read:

Is there any way to generate clock multiply by 4 using similar circuit apart from PLL?

ReplyDeleteHi

DeleteGood question, one of the ways is, of course, cascade two multiply-by-two circuits, satisfying the condition "The delay element’s delay must be less than half the input clock period; otherwise it will not work". But this will not work for all frequencies and will have a lot of limitations. The best way for frequency multiplication is to use PLL as far as I know.