Why clock gating checks not there in shift mode

Why there needs to be a lockup latch inserted because of DFT architecture reasons

First of all, we need to understand the basics of scan timing. A usual scan cycle looks pretty much like the one below. Tester sends shift data once every one cycle, and that usually is during clock low pulse. Image1 below shows typical scanin assertion and scanout observation during shift cycles. Here, I am showing both to be different, but usually they are done concurrently. during the same shift cycle, know obviously to save test time. Thus, every scan cycle consists of a positive and a negative edge.

|

| Image1: Shiftin and shiftout cycles |

Now, imagine a positive-edge triggered flop feeding to a negative edge-triggered flop. At the end of every scan cycle, both the flops will hold same data. Thus, the tester will not be able to provide "10" or "01" pattern on this pair. This may or may not result in a coverage drop, but it would result in a manual review of the logic to make sure there isnt any.

Similarly, during observation through scan out, tester will never be able to observe data on the output of negative edge flop, because of the redundancy of the data, resulting again in coverage drop.

Thus, the efforts are there to not have any such scenario in the first place during scan stitching. But if there are, a dummy scan element (or lockup latch) is put in place to elongate the data for one cycle. We need to note that doing this increases the scan chain length by 1, which is in contrary to other lockup latch cases. That is why, we are calling this as a dummy scan element.

Thus, now we know, why a positive edge triggered flop followed by a negative edge triggered flop needs a lockup element. Feel free to comment in case of any queries/feedbacks.

Why NMOS leads to a strong 0 and a weak 1

We frequently hear that an NMOS can pass a strong "0" and only a weak "1". Similarly, a PMOS can only pass a weak "1". But very few people actually know the reason behind this. In this post, we will delve into the details of why NMOS cannot pass a strong "1" and vice-versa.

To understand this, we have to dig deep into the behavior of MOS transistors.

|

| Figure 1: Basic MOS structure (NMOS) |

|

| Figure 2: NMOS channel as a resistor |

|

| Figure 3: Charges in NMOS with current flowing |

|

| Figure 4: Channel formation in NMOS in saturation region |

The limit of this behavior would be reached when Drain reaches a potential (Vg - Vth), thereby entire channel being infinitesimal. Upon trying to further raising voltage above this point, both drain and source would be cut-off. And further raising of voltage of Drain terminal beyond this point wont be possible. Thus, the maximum voltage the drain terminal can reach is Vs - Vth. In other words, a NMOS can never transmit an ideal "1". On similar terms, a PMOS wont be able to transmit an ideal "0" as well.

Does inserting lockup latch affect Logic Equivalence Check (LEC)

Logic equivalence check is normally carried out to ensure some processing of the design (example logic synthesis) has not resulted in change of functionality. It flags any logical changes with respect to a golden set of collaterals. There are many applications of logic equivalence checking, some of the prevalent ones pertaining to:

1. Logic equivalence check between RTL and corresponding synthesized netlist to ensure the logic synthesis has not introduced any functional issues

2. Logic equivalence check between two sets of netlists after doing netlist edits.

One thing to note here is that since RTL is the starting point here, LEC is done only for the logic present in the RTL, even for netlist vs netlist LEC (exceptions can be there). Other logic, such as scan chains are bypassed by application of certain constraints during LEC. For such logic, there are other methods to ensure correctness, such as scan tracing check to ensure there are no unintentional issues to trace scan chains.

Insertion of lockup latch also falls under non-functional netlist edits, hence not covered under LEC in normal scenarios. We must observe that fanout if lockup latch goes to scan_in pin of flop, which is not checked under LEC.

Analogy between English and C as a language

In our first post, we discussed that any programming language is a language in the first place. So it must be analogous to a language in how the constructs are used and formed in it. In this post, we will try to understand this aspect by making analogous comparison between English and C as a programming language.

As we know that any language has its character set as the most basic construct. English has Roman script as its character set, which includes a-z, A-Z. Similarly, to write a program in any programming language, you must be aware of the character set of that programming language.

The character set of C language is following:

– Alphabets (a-z, A-Z)

– digits (0-9)

– special symbols (any printable symbol like !,&,@,#) etc

In other words, any thing that can be printed forms the character set of C language. You can use these to form bigger constructs that we will discuss later.

Next, we know that in English, characters combine to make words, which have specific meanings. And these words may be of different categories viz nouns, pronouns, adjectives, adverbs etc. On a similar note, in C, we have variables, constants and keywords.

Similar to words combining to form sentences, C has commands/instructions. These instructions carry specific meanings and usually are related to either some task to do for the computer, or some message for the user.

Next in hierarchy, we have paragraphs or essays in English. On a similar note, we have programs in C that carry out a task on a whole. For instance, we might have a program to create a database which is a combination of multiple instructions.

Thus we have discussed how C is analogous to English, or any other language in terms of the constructs. I am pasting below the link of video from my YouTube channel in Hindi. You can go through it if you wish to.

Starting with C programming language

Before we start discussing about C as a programming language, we must be clear about the term programming language itself. Only then, we will be able to appreciate C as a programming language.

As the name suggests, programming language is a language. A language that computer understands, and that is used to interact with the heart of the computer. Obviously this language has to be understood by programmers as well, so that the interaction is understood by both the parties. In other words, through a programming language, you are giving instructions to the computer on the tasks it has to perform.

How programming language enables you to interact with computer is a bigger question. A computer does not directly understands the programming language, it understand only electrical signals (high voltage and low voltage, or in simpler terms 0 and 1, also called machine language). Although humans can interpret this coded language, but it is very inefficient and error prone. So we need a translator that converts this series of 0s and 1s into human readable version, the software that does this job is called a compiler or an interpreter based upon the method of translation used. C and other high level languages such as Java, Visual Basic etc are compiled languages, meaning that compiler is the heart of these languages. There are many compilers available for each programming language, for example C has turboC and GCC as compilers. You can understand these as products of different companies, which differ in their characteristics, services and ease of use they provide. But their basic task is to convert C code into computer under-standable 0s and 1s.

For our journey of talking about the basics of C, we will be using an online compiler programiz.com. I personally prefer online compilers because of the obvious benefits they provide; for example, you can access your code from multiple devices. You can use any compiler you wish, or you can use any other compiler as well.

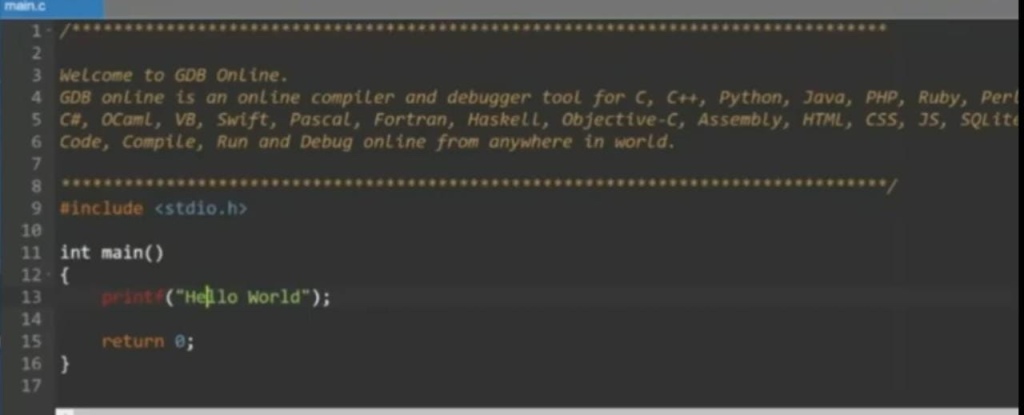

Most of the online compilers provide you with an option to have a pre written code segment, which you can use as a start point for your program. For instance, onlinegdb.com compiler gets you started with a default “Hello world!” printing program. Which you can modify as per your need. Typically, the first program anyone learns to execute in any programming language is to print hello world. We will also use the same to learn basic programming constructs of C language.

If you see the screenshot above, a typical C program has following constructs:

1. #include section: This section is used to include pre compiled C libraries to your code. These are already available C programs in machine language, to perform specific tasks. For example, studio.h enables you to get input from standard terminal and output to standard terminal as well.

2. Main() section: This is where the execution of a C program starts. Whatever your programs does has to be written directly or indirectly into this section (we will discuss more on this later). For instance, the statement printf is to display on screen, whatever is written within the double quotes. So, when this program executes, “Hello world” will be displayed on the screen.

So that concludes our first post, I hope we will have fun time learning C together. I am pasting below the video link from my YouTube channel in Hindi. You can go through it, if you wish to.

Welcome to glittering code

Hi there, I am a software professional with over a decade of industry experience. I am here to share my knowledge and experience with all of you, and in the process, learn a lot of things myself. As the saying goes, a good code is all that glitters. Let’s begin our journey to make our codes glitter.

How to interpret default setup and hold checks

Default Setup/hold checks - positive flop to negative flop timing paths

The launch/capture event of a positive edge-triggered flip-flop happens on every positive edge of the clock, whereas that of a negative edge-triggered flip-flop occurs on the negative edge of the flip-flop. In this post, we will discuss the default setup/hold checks different cases - same clock, 1:n clock ratio clock and n:1 ratio clock. And this should cover all the possible cases of setup/hold checks.

Case 1: Both flip-flops getting same clock

Figure 1 shows a timing path from a positive edge-triggered flip-flop to a negative edge-triggered flip-flop. Let us say the data is launched at instant of time "T", which is a positive edge. Then, the next negative edge following time "T" serves as the edge which captures this data; thus forming the default setup check. And the very previous negative edge serves as the hold check. This is shown in the first part of figure 1. Thus, in this case, both setup and hold checks are half cycle.

Setup and hold slack equations

Setup slack = Period(clk)/2 + Tskew - Tclk_q - Tcomb - Tsetup

Hold slack = Period(clk)/2 + Tclk_q + Tcomb - Tskew - Thold

Case 2: Flip-flops getting clocks with frequency ratio N:1 and positive edge of launch clock coincides with negative edge of capture clock

One of the cases where this happens is when clock is divided by an even number. Another is when odd division is followed by inversion. The resulting waveform will be as shown in figure 2. In this case, each positive edge of launch flip-flop is capable of launching a fresh data, but will be overwritten by next data. Only the one which is launched on the positive edge closest to the negative edge of capture clock will get captured at the endpoint. Similarly, the data which is launched at the edge coinciding negative edge of capture clock must not overwrite the data captured at the same edge. The setup and hold checks, thus formed, are as shown in figure 2 below. The setup check is full cycle of launch clock, whereas hold check is a zero cycle check.

Setup and hold slack equations

Setup slack = period(launch_clock) + Tskew - Tclk_q - Tcomb - Tsetup

Hold slack = Tclk_q + Tcomb - Tskew - Thold

Case 3: Flip-flops gettings clocks with frequency ration N:1 and positive edge of launch clock coincides with positive edge of capture clock

One of the cases where this happens is when capture of the data happens on an odd divided clock. The resulting setup and hold checks are as shown in figure 3. Both setup and hold checks are half cycle of faster launch clock.

Setup and hold slack equations

Setup slack = period(launch_clock)/2 + Tskew - Tclk_q - Tcomb - Tsetup

Hold slack = period(launch_clock)/2 + Tclk_q + Tcomb - Tskew - Thold

Case 4: Flip-flops getting clocks with frequency 1:N and positive edge of launch clock coincides with negative edge of capture clock

One of the cases is when division is performed after inversion of the master clock and data is launched on the divided clock. Figure 4 shows the default setup/hold checks for this case. In this case, setup check is equal to full cycle of faster clock and hold check is a zero cycle check.

Setup and hold slack equations

Setup slack = period(capture_clock) + Tskew - Tclk_q - Tcomb - Tsetup

Hold slack = Tclk_q + Tcomb - Tskew - Thold

Case 5: Flip-flops getting clocks with frequency 1:N and positve edge of launch clock coincides with positive edge of capture clock

This is a case of even division, or inversion, followed by odd division, followed by inversion. The setup and hold checks, both are equal to half cycle of faster clock.

Setup and hold slack equations

Setup slack = period(capture_clock)/2 + Tskew - Tclk_q - Tcomb - Tsetup

Hold slack = period(capture_clock)/2 + Tclk_q + Tcomb - Tskew - Thold

Can you think of any other scenario of setup/hold checks for this case? Please feel free to share your views.

Clock relationship between reset synchronizer and fanout flip-flops

Design problem: Reset synchronizer clock for multi-frequency flip-flops in fanout

|

| Figure 1: Reset synchronizer |

|

| Figure 2: Reset synchronizer works on positive edge of 100 MHz clock |

|

| Figure 3: Reset synchronizer works on positive edge of 200 MHz clock coinciding with positive edge of 100 MHz clock |

|

| Figure 4: Reset synchronizer works on positive edge of 200 MHz clock coinciding with negative edge of 100 MHz clock |

Now, let us explore the last option; i.e., reset synchronizer working on negative edge of 100 MHz clock. In this case, as shown in figure 5, both 100 MHz and 200 MHz flip-flops come out of reset on same edge. Thus, this case works perfectly. Figure 5 illustrates this.

|

| Figure 5: Reset synchronizer works on negative edge of 100 MHz clock |

Can you provide any other solution that is possible and better than ones discussed here.

Data check timing paths

Constraining data-check timing paths: To constrain data-check timing paths, we first need to ensure that there is a data-check associated with the signals in question. It can either be defined in the timing model being picked or we can define using SDC construct "set_data_check". Once data check is defined, we can simply ensure that both the reference signal and constrained signal are launched from same clock or related clock to see data-check timing path reported.

Clock gating timing paths

- The endpoint is the "EN" pin of Integrated Clock Gating (ICG) cell OR

- The endpoint is one of the input pins of a combinational cells with at least one of the other pins getting a clock signal

Why is the sum of setup time and hold time always positive

Reg-to-out paths

Constraining with virtual clock is helpful when we know that the data-path budgeting is exclusive of clock path, for instance, a sub-design of an SoC. A virtual clock is a clock without any source. So, data-path outside the block can be modeled using "set_output_delay" with respect to virtual clock and clock path outside the block can be modeled using "set_clock_latency" for virtual clock. The steps are listed below:

- "create_clock" at clock source : CLK

- "create_clock" without a clock source : VCLK (virtual clock)

- set_output_delay at output port with respect to VCLK

When we know that the outside data path delay and clock path delay are fixed, then we can constrain the port with respect to real clock itself. The steps are listed below:

- "create_clock" at clock source : CLK

- "set_output_delay" at output_port with respect to CLK (or with respect to a clock related to CLK)

In-to-reg paths

Constraining with virtual clock is helpful when we know that the data-path budgeting is exclusive of clock path, for instance, a sub-design of an SoC. A virtual clock is a clock without any source. So, data-path outside the block can be modelled with "set_input_delay" with respect to virtual clock and clock path outside the block can be modeled using "set_clock_latency" for virtual clock. The steps are listed below:

- "create_clock" at clock source

- "create_clock" without any source (virtual clock)

- set_input_delay at input_port with respect to virtual clock created

When we know that the outside data path delay and clock path delay are fixed, then we constrain the input port with respect to real clock itself. An example is SoC level protocol signals such as ethernet signals. The input port is constrained either with respect to the same clock going to the endpoint or some clock related to it. The steps are listed below:

- "create_clock" CLK at clock source

- "set_input_delay" at input_port with respect to CLK (or with respect to a generated_clock created from the CLK

Reg-to-reg paths

- Flop-to-flop paths: Both startpoint and enpoint are edge-triggered (flops). See Setup and hold checks for flop-to-flop paths

- Flop-to-latch paths: Startpoint is edge-triggered and endpoint is level-sensitive. See setup and hold checks for flop-to-latch paths

- Latch-to-flop paths: Startpoint is level-sensitive and endpoint is edge-triggered. See setup and hold checks for latch-to-flop paths

- Latch-to-latch paths: Both startpoint and endpoint are level-sensitive. See setup and hold checks for latch-to-latch paths

- All the components of a timing path we discussed in timing paths, i.e. startpoint, endpoint, launch clock path, capture clock path and data path exist for a reg-to-reg path.

- To constrain reg-to-reg paths, we just have to ensure that both the startpoint and endpoint receive a valid clock signal and there is no timing exception (such as false path between the clocks) masking the timing path.

Timing path types

|

| Figure 1: Generic timing path |

In-to-reg path: The timing path where "startpoint" is an input port and "endpoint" is a sequential element, is termed as in-to-reg path.

Reg-to-out path: Here, "startpoint" is a sequential element and "endpoint" is an output port.

In-to-out path: In this type of path, "startpoint" is an input port and "endpoint" is and output port.

Clock gating paths: In this type of path, "startpoint" can be any out of sequential element, input port or output port. The endpoint is usually input pin of either a combinational gate or an Integrated Clock Gating cell (ICG). The common scenario involved is to time the arrival of constrained signal (termed as enable in clock gating paths) such that complete pulses of clock as reference signal are transmitted and there is no glitch at the output of the "endpoint".

Min-pulse-width-check paths: Here, both reference and constrained path, both are clock paths and common right from source till "endpoint". This type of path compares the latest arrival of rise transition of the clock with respect to the earliest arrival of fall transition of clock and vice-versa. The nature of check is max check only.

Data check paths: In this type of paths, both reference signal and constrained signal are data launched by a clock signal.

Point-to-point paths: The paths with only constrained signal are called as point-to-point paths. "startpoint" as well "endpoint" can be any sequential or combinational pin or port.

Timing paths

A timing path can be supposed to be consisting of two sub-paths - a reference path through which reference signal traverses and a constrained path through which constrained signal traverses. Both of these essentially originate from same source (or have a definite relationship at their respective sources). At the terminal end of both, there is a relationship governing the arrival of constrained signal to the arrival of reference signal. Depending upon the type of reference signal and constrained signal, the type of elements encountered by these and the check that is formed between the two, we govern the type of path. For instance, in a reg-to-reg setup path, the reference signal is clock, constrained signal is data launched from a clock and traversing through a flip-flop and the check that is formed between the two signals is a setup check at a flip-flop as the endpoint.

|

| Figure 1: Generic timing path in STA |

Based upon type of check being formed between constrained signal and reference signal, there are commonly two types of paths that are formed: max path/setup check path and hold check path/min path.

Max/setup check path: In this kind of path, the earliest arrival of reference signal and latest arrival of constrained signal is considered. The kind of check is known as setup check in most of the cases. And the type of path is called setup path/max path.

Min/hold check path: In this kind of paths, the earliest arrival of constrained signal and the latest arrival of reference signal is considered. The kind of check is known as hold check in most of the cases. And the type of path is called hold path/min path.

Let us move to the commonly perceived understanding of a timing path by taking an example of a reg-to-reg path. Figure 1 below shows an example of a timing path, which starts from a flip-flop and ends at a flip-flop.

|

| Figure 2: Components of a reg-to-reg path |

The above timing path (or any timing path, in general), has following components:

Startpoint: The element from which the data gets launched is known as startpoint. In general, it can be a sequential element (latch, flip-flop) or an input port. In case it is a flip-flop, the clock pin of the flip-flop is counted as the startpoint of timing path. For point-to-point paths, it can also be a combinational input or output pin.

Endpoint: The element at which timing path ends is called the endpoint. It can be data pin of flip-flop or an output port. For point-to-point paths, it can also be a combinational input or output pin.

Clock: Most of the timing paths are constrained by a clock signal, which clocks both startpoint and endpoint. The properties of the clock signal, such as clock period, jitter etc are defined in timing constraints.

Launch clock path: It refers to the path traversed by clock signal from clock source to the startpoint.

Capture clock path: It refers to the path traversed by clock signal from clock source to the endpoint.

Data path: It refers to the path traversed by data signal from starptoint to endpoint.

In the above example, launch clock path and data path together constitute constrained signal path and capture clock path constitutes reference signal path.