As we know, all flip-flops which are required to be "out of reset" at the same time are placed in fanout of a single reset synchronizer. In this post, we will discuss if there is any relationship required between clock frequency of reset synchronizer and the clock frequency of the flip-flops in fanout. For now, let us assume that all the flip-flops in the fanout of reset synchronizer work on a single clock "CLK". <dsfdsf> discussed the case when the flip-flops are working on multiple clocks.

Let us first assume that reset synchronizer's clock period is N*CLK_PERIOD; i.e. reset synchronizer gets a DIVIDE_BY_N clock of the flip-flops' clock. Figure 1 below shows the setup check from a clock with period N*CLK_PERIOD to a clock with period CLK_PERIOD. Since, all the flip-flops have same setup check being formed, all will get out of reset at the same edge; thus, fulfilling the requirement.

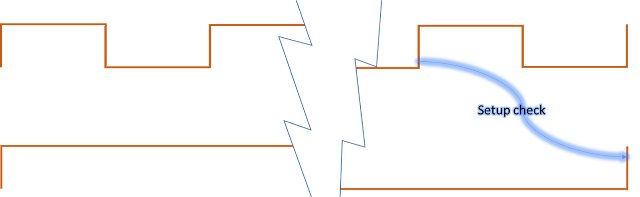

Similarly, there is a definite setup check from a clock with period CLK_PERIOD/N to a clock with period CLK_PERIOD as shown in figure 2 below. Thus, if reset synchronizer works on clock with frequency "N" times the flip-flops in fanout, we get all the flip-flops out of reset at same time, thereby, fulfilling the requirement again.

Thus, we see that if all the flip-flops in fanout of reset synchronizer work on a single clock, there is no relationship required between frequency of reset synchronizer and frequency of fanout flip-flops as long as we meet the setup and hold requierements. However, this is not true when flip-flops work on multiple clocks as discussed in <SDFDSF>.